The Synopsys HPC Design Kit, a key component of the Synopsys Foundation IP portfolio, is an add-on to the Duet Package of Embedded Memories and Logic Libraries. Developed in close collaboration with leading CPU, GPU, and DSP IP providers—including Imagination Technologies and CEVA—the HPC Design Kit offers a comprehensive suite of high-speed, high-density memories and logic libraries. This enables SoC designers to optimize processor cores for maximum speed, minimal area, lowest power consumption, or the ideal balance of these attributes to suit their specific application requirements. Featuring optimized standard cells and SRAMs, the HPC Design Kit allows designers to enhance all processors within an SoC using a single package, thereby reducing design costs and accelerating time-to-market. In addition, optimized reference flows and expert core implementation services are available to support design teams in achieving their processor and SoC design objectives as efficiently as possible.

Highlights

- One design kit for optimizing all processor cores on an SoC

- Includes ultra high-density memory compiler and more than 125 new standard cells and memory instances

- Up to 10% performance improvement, 10% area and 15% power reduction on DSPs like CEVA-XC DSP core

- Up to 10% performance improvement on CPU cores

- Up to 25% lower power with 10% area reduction on Imagination GPU cores such as the Imagination Technology PowerVR Series6 IP core

The HPC Design Kit is fully integrated with Synopsys EDA tools for efficient design and supports a broad range of process nodes and operating conditions. This makes it easier for customers to achieve the best possible PPA and seamless integration across various computing applications.

The HPC Design Kit allows SoC designers to optimize the Synopsys Embedded Vision (EV) Processor’s vector DSPs and convolutional neural network (CNN) engines. Depending on the requirements of the target application, designers using the HPC Design Kit for EV can optimize their implementation to achieve a 39% power reduction, a 10% reduction in area, or a 7% performance boost for their SoCs.

To learn more, read the article Optimizing PPA for HPC & AI Applications with Synopsys Foundation IP.

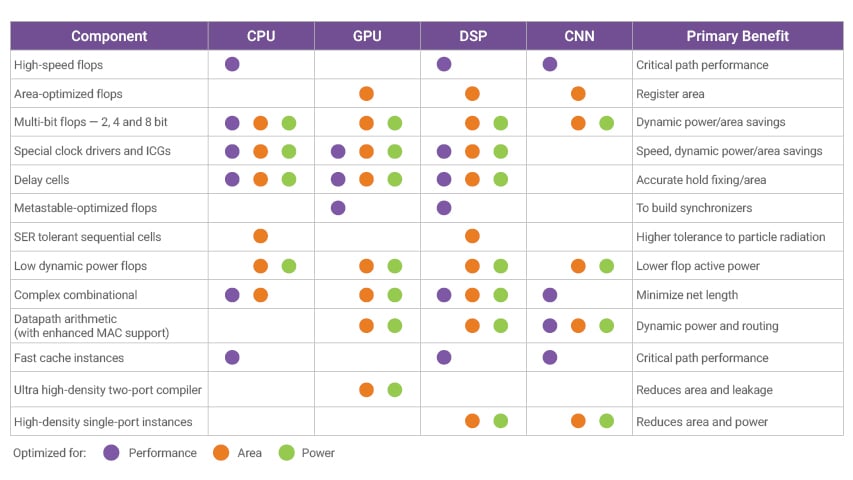

HPC Design Kit Component Summary

Find Your IP

Search for IP

Quickly identify and access the right IP solutions for your project needs.

Foundation IP Selector

Find embedded memory and logic IP for your SoC design.

Non-Volatile Memory IP Selector

Find silicon-proven NVM IP for your SoC design needs.