Synopsys ARC 625D Processor Core

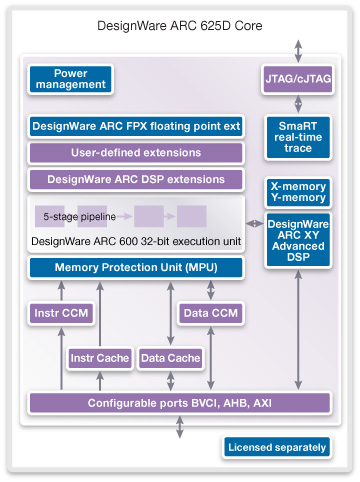

The Synopsys ARC® 625D processor core is highly configurable and ideal for embedded application where high-performance and low-power is required. Instruction and data cache memories ranging from 2 KB - 32 KB allow designers to configure the processor core at build time to improve the efficiency and performance of the microprocessor. The processor core is designed as a complete solution for system-on-chips (SoCs) targeted at consumer, networking, automotive and other applications.

The Synopsys ARC 625D processor core's flexible, configurable memory architecture makes it ideal for applications running an embedded RTOS. Powerful digital signal processing (DSP) options enable designers to implement more functionality eliminating separate logic or DSP blocks from the SoC. User-defined extensions offer the flexibility to add instructions, registers, flags and condition codes, enabling the creation of a processor core that is highly tuned for the specific application. The ARC 625D processor core also supports an optional Floating Point Unit (FPU) that supports single precisions, double precision, or both computation requiring only 10% the area of a typical FPU coprocessor.

The Synopsys ARC 625D processor core has an optional memory protection unit (MPU) that gives the software running on the processor core the ability to control access rights to the memory. This improves performance by preventing processes running on the processor from accessing memory that is not allocated to them. The optional Power Management Unit (PMU) allows software control over clocking and the processor core voltage level, enabling dynamic power consumption management. There are also a number of multiplier options available with the processor core including a single-cycle 16x16 multiplier, and single- and multiple-cycle 32x32 multipliers that reduce power consumption and silicon area.

The ARC processor is designed with a 16-/32-bit instruction set architecture that provides high code density with no overhead for switching between 16- and 32-bit instructions. With flexible addressing modes, the ARC 625D provides up to 128 dual or single operand instruction codes available for user-defined instructions and up to 64 directly addressable core registers and 32 conditional execution codes.

The ARC 625D processor core is supported by a full suite of software and hardware development tools. The suite includes the acclaimed MetaWare Development Kit that generates highly efficient code ideal for deeply embedded applications, the ARC simulators including xCAM and nSIM, and the ARChitect configuration tool.

Register for the ARC 600 Processor Online Training

- 5-stage instruction pipeline

- Static branch prediction

- 32-bit data, instruction and address buses

- Configurable instruction cache, 2 KB - 32 KB

- Configurable data cache, 2 KB - 32 KB

- Scoreboarded data memory pipeline to reduce stalls

- Single-cycle instruction CCM (Closely Coupled Memory), 1 KB - 512 KB

- Single-cycle data CCM, 2 KB - 256 KB

- Up to 32, two level interrupts

- Up to 128 dual or single operand instruction codes available for user-defined instructions

- 16 or 32 entry register file in base core, extendible to 60 registers

- 16- and 32-bit MUL and MAC instructions

- Saturating arithmetic instructions

- Zero overhead loop support

- Full DSP performance using configurable banks of XY memory

- Optional Floating Point Unit

- Sleep mode via software instruction

- Clock gating option

- Debug host can access all registers and CPU memory

- Supported by leading debuggers including Green Hills Software and MetaWare®

| Description: | ARC 625D 32-bit embedded processor core with cache, optional MPU, DSP, FPU |

| Name: | dwc_arc_625d_core |

| Version: | 4.9b |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_ARC600_Series_bundle |

| Product Code: | 8022-0, 8023-0, 8024-0, 8025-0, 8045-0, 8046-0, 9839-0 |